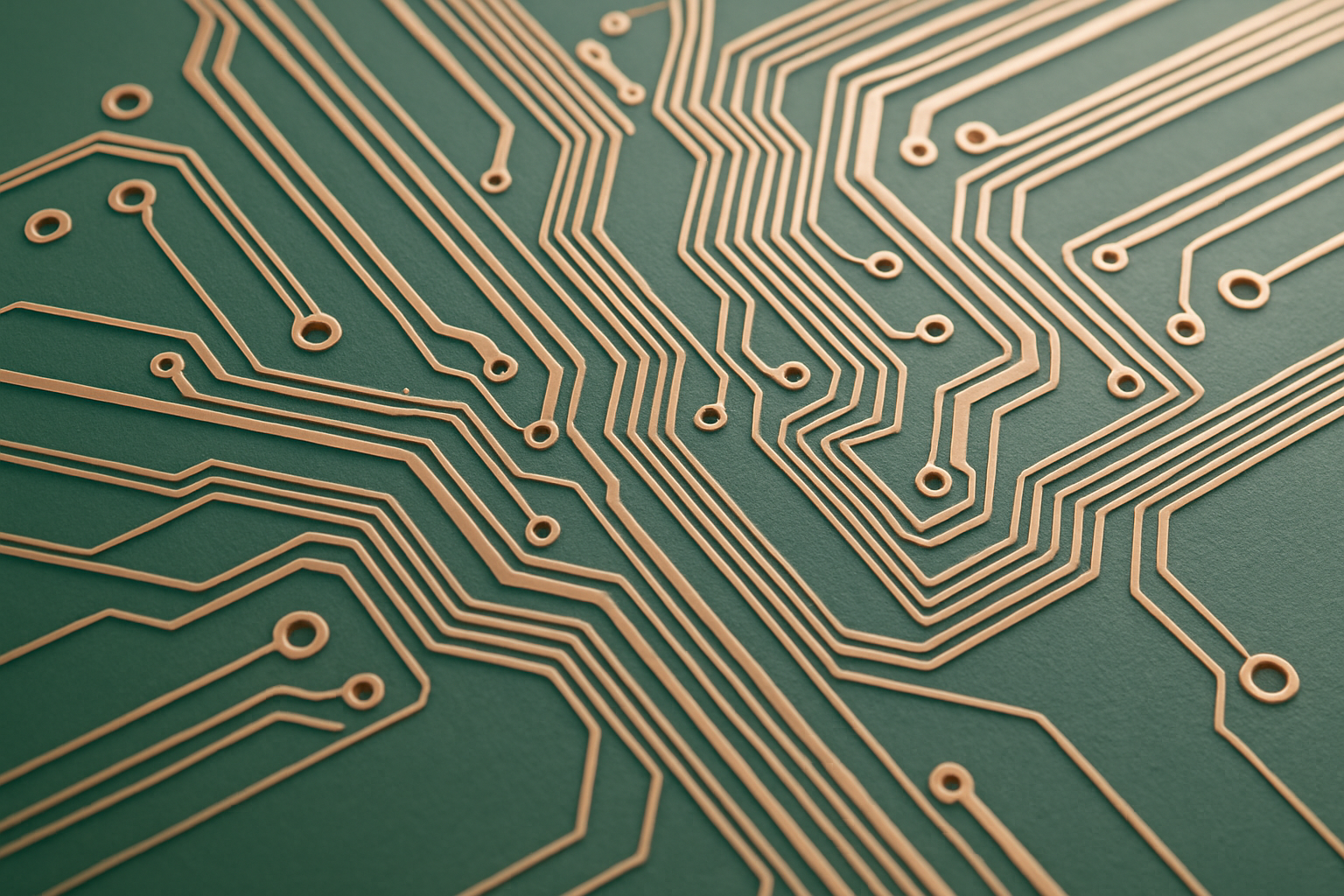

Leiterplattenentflechtung

Was ist eine Leiterplattenentflechtung?

Leiterplattenentflechtung bezeichnet den Schritt im PCB-Layout, in dem die elektrischen Verbindungen zwischen Bauteilen als Leiterbahnen auf den Kupferlagen „verlegt“ werden. Aus Sicht der Planung geht es darum, dass jede Verbindung ihren passenden Weg findet – ohne Kollisionen, ohne unnötige Umwege und unter Einhaltung technischer Regeln.

Anschaulich lässt sich das mit einer Stadtkarte vergleichen: Bauteile sind „Gebäude“, elektrische Netze sind „Straßenverbindungen“. Die Entflechtung sorgt dafür, dass alle Ziele erreichbar sind, Hauptstraßen ausreichend breit sind und Kreuzungen (z. B. Layerwechsel durch Vias) sinnvoll gesetzt werden.

Wofür wird Leiterplattenentflechtung eingesetzt?

Leiterplattenentflechtung wird überall dort eingesetzt, wo aus einem Schaltplan eine real herstellbare Leiterplatte werden soll. Typische Einsatzfelder sind:

- Prototypenentwicklung: schnelle, aber dennoch regelkonforme Umsetzung des Routings für erste Funktionsmuster.

- Serienprodukte: Optimierung auf reproduzierbare Fertigung, Prüfkonzepte und stabile elektrische Eigenschaften.

- Leistungselektronik: kurze, breite Strompfade, definierte Rückstromwege und thermisch sinnvolle Führung.

- Schnittstellen- und Kommunikationsdesign: kontrollierte Impedanzen, definierte Längen und sauberes Paar-Routing (z. B. bei Hochgeschwindigkeitssignalen).

Wie funktioniert Leiterplattenentflechtung in der Praxis?

In der Praxis beginnt die Entflechtung nach dem Platzieren der Bauteile. Wir betrachten dabei nicht nur „ob“ eine Verbindung möglich ist, sondern „wie“ sie sinnvoll umgesetzt wird. Übliche Schritte sind:

- Regeln festlegen: Leiterbahnbreiten, Abstände, Via-Typen, Kupferlagenaufbau, ggf. Impedanzvorgaben und Fertigungsrestriktionen.

- Priorisieren: kritische Netze zuerst (z. B. Takt, Datenleitungen, Strompfade), weniger kritische Verbindungen danach.

- Führen der Leiterbahnen: möglichst kurze, klare Wege, sinnvolle Layerwechsel, Vermeidung unnötiger Schleifen.

- EMV- und Rückstrompfade berücksichtigen: zusammenhängende Bezugslagen, definierte Masseführung und durchdachte Platzierung von Entkopplung.

- Fertigungsgerechtigkeit prüfen: Einhaltung von Mindestabständen, sinnvolle Via-Strategie, ausreichende Reserven für Prozessschwankungen.

- Finale Checks: Design-Rule-Check (DRC) sowie – je nach Projekt – zusätzliche Prüfungen wie Signalintegrität/Impedanz, thermische Aspekte oder DFM-Checks.

Die Qualität der Entflechtung zeigt sich oft erst später: bei der Inbetriebnahme (Störfestigkeit), in der Serie (Ausschuss/Prozessfenster) oder im Feld (Zuverlässigkeit).

Warum ist Leiterplattenentflechtung für Unternehmen relevant?

Für Unternehmen ist Leiterplattenentflechtung relevant, weil sie direkt Einfluss auf Time-to-Market, Kosten und Zuverlässigkeit hat:

- Weniger Iterationen: Ein sauber entflechtetes Layout reduziert die Wahrscheinlichkeit von Re-Designs, Zusatzschleifen und wiederholten Prototypenläufen.

- Planbare Fertigungskosten: Routing-Entscheidungen beeinflussen Layeranzahl, Via-Dichte und Fertigungsanforderungen – und damit Stückkosten und Lieferzeiten.

- Qualität und Robustheit: Gute Masse-/Rückstromführung und passende Abstände verbessern EMV-Verhalten und senken Ausfallrisiken.

- Testbarkeit: Wenn Testpunkte, Netzzugänglichkeit und klare Strukturen früh berücksichtigt werden, lassen sich Prüfkonzepte später effizienter umsetzen.

Im Zusammenspiel von Layout, Fertigungsanforderungen und Prüfstrategie ist die Leiterplattenentflechtung damit ein zentraler Hebel, um Entwicklungsziele sicher in eine reproduzierbare Umsetzung zu überführen. Im Kontext unserer Leistungen in der Elektronikentwicklung ist die Entflechtung ein wichtiger Schritt, um aus dem Schaltplan ein fertigungsgerechtes Design abzuleiten.